VLSI Verification Engineer Interview Guide 2026 (India)

TL;DR. Verification interviews in India in 2026 test three things: SystemVerilog + UVM depth, debug instinct, and whether you've shipped real work. Syntax questions get you through round 1. A strong project deep-dive and clean debug thinking are what get you the offer at Intel, Qualcomm, NVIDIA, Broadcom or Cadence. This is the exact prep plan I give engineers I mentor.

I ran UVM verification teams at Qualcomm for six years. I've interviewed over 400 candidates across levels, from fresh graduates to staff engineers. Verification has the most hiring volume in Indian VLSI right now — roughly 2x the openings of RTL design, based on our current verification job board. That does not mean it's easy to get in. The bar at product companies is steep, and most candidates fail the same three things in the same three ways.

Let me tell you what those are, and how to actually prepare.

What verification interviewers actually test

Verification interviews are not software interviews. There is no LeetCode. There are no dynamic programming gotchas. What interviewers at product companies test for, in rough order of weight:

- SystemVerilog depth (30%). Classes, randomization, constraints, interfaces, clocking blocks. Not syntax trivia — applied understanding.

- UVM fluency (25%). The full methodology. Phases, factory, config DB, sequences, TLM. Not memorized slides. You need to explain why each piece exists.

- Debug and problem decomposition (20%). Given a failing testbench, where do you look? How do you narrow scope? This is often the differentiating round.

- Protocol and architecture knowledge (15%). AXI, APB, PCIe, UCIe, memory protocols. Enough to verify them, not design them.

- Project deep-dive (10%). Can you walk through what you actually built, with specifics? This is where most 3-5 year candidates lose the offer.

Coding-only prep is how freshers prepare. Senior candidates who prep that way get rejected. Your project story is the differentiator by year 3.

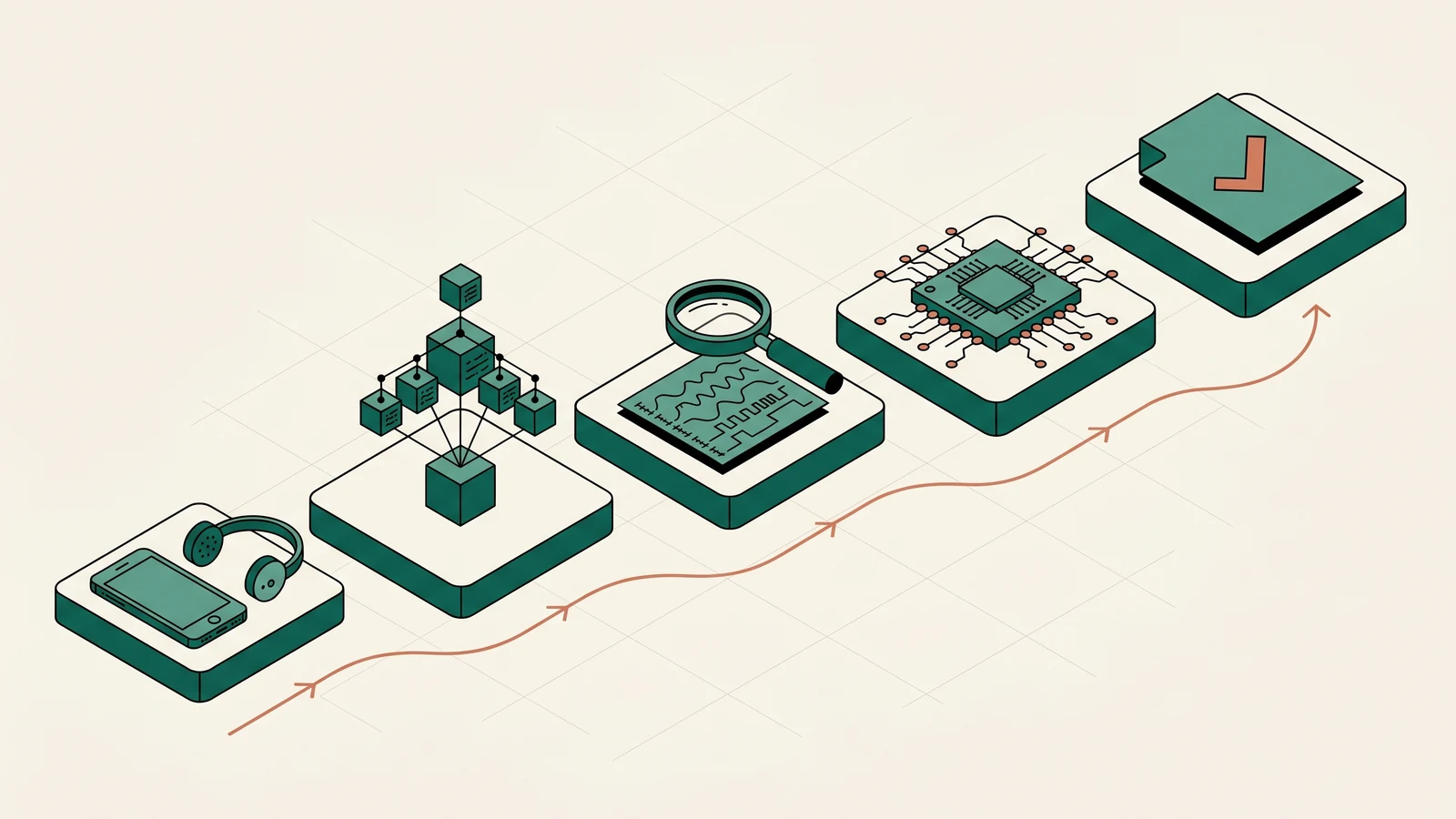

The UVM architecture every verification interview Round 2 will reference — know every block and its responsibility.

The typical interview structure at product companies

Round counts and names vary, but here's the normalized structure I've seen across Intel, Qualcomm, NVIDIA, Broadcom, and Cadence:

Round 1: Technical screen (45-60 min)

Usually a phone or video call with a senior engineer. Sanity check on fundamentals.

- Digital design basics — FSMs, setup/hold, CDC, metastability

- Basic SystemVerilog — data types, arrays, what a class is, what randomization does

- Basic UVM — sequencer, driver, monitor, agent, scoreboard — why they exist

- A short coding question, often "write a transaction class for a memory protocol" or "write a constraint that generates aligned addresses"

Rejection rate here is brutal. For 3-5 year candidates, the screener is not looking for brilliance — they are looking for "does this person actually know what UVM is or did they just put it on their resume."

Round 2: UVM and SystemVerilog deep dive (60-90 min)

The serious round. You'll be asked to walk through a UVM testbench architecture for a block you've worked on. Expect questions like:

- "Explain the UVM phasing for your last testbench. Why do we need the reset phase separately?"

- "How do you handle config DB collisions when two components set the same key?"

- "Your sequence is stuck — walk me through how you'd debug it."

- "Write constraints for generating a random burst transaction with address alignment, length distribution, and a 10% probability of illegal ID."

Depth wins this round. Interviewers can tell within 10 minutes whether you understand UVM or just use it.

Round 3: Debug and functional coverage (60-90 min)

You'll be shown a failure log, a waveform, or a coverage hole and asked to diagnose. This is the round that separates candidates who will contribute in 3 months from those who will need 12.

- "This test is hanging. Here's the log. What's your first move?"

- "Here's a coverage report. We have 87% functional coverage but 62% on this specific cover group. How do you close the gap?"

- "The scoreboard is reporting a mismatch on write-back transactions. Walk me through the debug."

Prep advice: stop practicing syntax. Start practicing debug. Pick an open-source UVM testbench, break it on purpose, and fix it. This is 10x more valuable than memorizing UVM factory patterns.

Round 4: Project deep-dive + behavioral (60 min)

You'll be asked to pick one project and explain it end-to-end. Architecture diagram on the whiteboard. Specific challenges. Specific tradeoffs you made. Specific metrics you hit.

The killer question: "Tell me about a bug you found that the designer pushed back on."

If you have nothing specific to say here, you're a junior engineer regardless of your years of experience. Every real verification engineer has this story. Find yours and practice telling it in 3 minutes.

Round 5: HR and offer (30 min)

CTC discussion, timeline, team fit. By this point the technical decision is made. This round rarely changes outcomes but can change comp.

25 real verification interview questions, with answers

These are representative of what I've both asked and been asked in the last three years. I've split them by theme.

SystemVerilog fundamentals

1. What's the difference between logic and reg in SystemVerilog?

Both are 4-state types. logic is a SystemVerilog type that can be driven by a single driver and used in either always_comb, always_ff, or continuous assignment. reg is a Verilog legacy type that carries no synthesis semantics. Use logic in all new SystemVerilog. Never mix reg and logic on the same signal.

2. What does rand vs randc do?

Both randomize, but randc cycles through all possible values before repeating. Use rand for most fields. Use randc when you need enumerated coverage — like cycling through all opcodes before repeating.

3. When would you use a mailbox vs a queue?

Queue is a local data structure. Mailbox is a built-in synchronization primitive with blocking put and get semantics. Use mailbox for cross-thread communication. Use queue for simple local buffering within a class.

4. What's a clocking block and why does it matter?

A clocking block synchronizes testbench signals to a specific clock edge, eliminating race conditions between TB and DUT. Without clocking blocks, your testbench can sample in the same delta cycle as the RTL driver, causing flaky tests. Always use clocking blocks in interfaces.

5. Explain fork/join, fork/join_any, fork/join_none with a use case for each.fork/join waits for all threads — use for parallel bus transactions that must all complete. fork/join_any waits for the first — use for timeout patterns (fork the test, fork a timeout, proceed on whichever finishes first). fork/join_none doesn't wait at all — use for detached monitors that run in the background.

UVM depth

6. Walk through the UVM phases in order.

Build, connect, end_of_elaboration, start_of_simulation, run (which includes reset, configure, main, shutdown), extract, check, report, final. The run phase is the only one that consumes simulation time. Pre-run phases are for building architecture. Post-run phases are for checking.

7. Why do we need the factory override mechanism?

Factory overrides let you replace a component or transaction type at runtime without modifying the original code. Critical for creating test-specific variants — a corrupt driver, a different scoreboard policy — without forking your testbench. It's the main reason UVM is more reusable than raw OOP SystemVerilog.

8. What's the difference between uvm_config_db and uvm_resource_db?

Resource DB is the underlying storage. Config DB is a scoped wrapper with hierarchical context. Always use config_db — it gives you path-scoped visibility and matches the testbench hierarchy. Resource_db is legacy and almost never correct in modern code.

9. How does sequencer-driver handshaking work?

The driver calls get_next_item, which blocks until a sequence sends a transaction. Driver processes, calls item_done. For pipelined protocols, use get and put instead so you can have multiple in-flight transactions. Every new verification engineer gets this slightly wrong — practice it.

10. Your testbench is hung at run phase. No output. What do you check first?

In order: (1) Reset applied? Many TBs hang because reset was never asserted. (2) Clock toggling? Check if the clock generator is actually connected. (3) Sequence started? The sequencer might be idle because no test called start_item. (4) Objections not dropped? A test that never calls drop_objection will run forever. Senior engineers check objections third. Juniors check them last.

Coverage and verification strategy

11. Difference between functional and code coverage.

Code coverage tells you what RTL lines executed. Functional coverage tells you what scenarios your testbench exercised. 100% code coverage with 50% functional coverage means you ran the code but didn't actually verify the features. Both matter. Functional coverage is the harder problem.

12. Your coverage shows 90% but a field-found bug exposed a missed scenario. What was wrong with your coverage plan?

Coverage plans miss scenarios when they only cover the spec, not the implementation. Review the bug's trigger condition and add a cover point that would have hit it. This is how you build good coverage intuition over a career.

13. How would you verify a block with a 128-entry FIFO where each entry has an 8-bit tag?

Can't exhaustively verify. Use coverage-driven strategy: cover points on fill levels (empty, half, full, almost-full), tag ranges, and specific boundary transitions (empty-to-one, full-to-not-full). Constrained random on traffic. Directed tests on the corner cases coverage flags as hard to hit.

Protocol and architecture

14. Draw a minimal AXI4 write burst. What must the slave respond with, and when?

Master sends address on AW channel, data on W channel with WLAST on final beat. Slave responds on B channel with OKAY/SLVERR/DECERR after receiving the last data beat. Slave cannot respond before all data is received. Interviewers will ask about early-response bugs — they're common in junior work.

15. What's the difference between AXI4 and AXI4-Lite?

AXI4 is full burst-capable. AXI4-Lite supports single-transfer, no bursts, no out-of-order. Use AXI4-Lite for register files and low-bandwidth control paths. Use full AXI4 for memory interfaces and high-bandwidth data.

16. Why do you need outstanding transaction tracking in a verification environment?

If the DUT supports multiple outstanding transactions (e.g., AXI with ID-based reordering), your scoreboard needs per-ID tracking. A simple in-order queue will falsely report mismatches when the DUT legally returns responses out of order.

Debug scenarios

17. Your scoreboard reports a mismatch. The RTL team says their block is correct. How do you proceed?

First: reproduce with a directed test. Second: dump both expected and actual values at the scoreboard input. Third: trace back one level at a time — is the reference model wrong, or is the transaction being modified between monitor and scoreboard? Never accept "our RTL is correct" at face value. Never assume your testbench is correct either. Disprove one of them with data.

18. A test passed in one regression but fails in the next. What's your first move?

Check the seed. Check the tool version. Check any recent testbench changes. Run the failing seed alone with +UVM_VERBOSITY=UVM_HIGH. Regression flakiness is usually a missing synchronization between testbench and RTL — clocking block mismatch, race on reset, or a monitor sampling at the wrong edge.

19. Coverage-driven verification isn't closing. You've hit 94% and stuck. What's your strategy?

Move to targeted directed tests for the remaining 6%. Cover holes at 94%+ are almost always conditional scenarios that constrained random won't naturally generate. Write explicit tests. Don't burn compute trying to brute-force the tail.

Career / behavioral

20. Tell me about a bug you found that the designer pushed back on.

Have a real story. Specifics: the block, the symptom, the waveform, the evidence you gathered, the conversation, the resolution. This question differentiates real verification engineers from resume-pattern matchers.

21. Why did you choose verification over RTL design?

Don't say "more openings" even if that's true. Say something specific: you like debug more than design, you enjoy thinking about what can break more than what should work, you're drawn to the systems-level view. Make it real.

22. Walk me through your most recent project.

Architecture diagram. What was the block. What was your testbench structure. What tools. What did you catch. What metric you hit. Practice telling this in 3 minutes with a clear arc. Most candidates ramble for 15.

23. How do you handle a disagreement with a senior engineer on verification strategy?

Bring data. Write a quick experimental proof. Show the numbers. If you're right, they'll see it. If you're wrong, you'll learn. "Bring data" is the only answer that works in a technical organization.

24. Describe a time you missed a bug.

Real story. What was missed, why the coverage plan didn't catch it, what you changed about your process. Humility + specifics + what you learned. Never say "I've never missed a bug." That's a red flag.

25. Where do you see yourself in 5 years?

For a 3-5 year engineer: "Leading a verification team on a chip tapeout, owning end-to-end methodology for a block or subsystem." Specific. Ambitious but realistic. Not "I want to learn more."

Tools they'll ask about

Expect deep questions on whichever simulator your target company uses. Pick one and know it cold:

- Synopsys VCS — most common at Qualcomm, Broadcom, AMD. Know

+UVM_VERBOSITY,+ntb_random_seed,-sv_libfor DPI. - Cadence Xcelium — dominant at Cadence, Intel, Nvidia. Know

-coverage, IMC for coverage analysis. - Mentor Questa — common at service companies and some automotive. Know Visualizer for debug.

You don't need to know all three. You need to know one of them to the point where you can explain its debug flow, coverage model, and regression setup without looking at documentation.

For a broader tools guide relevant to physical design too, see our EDA tools for physical design 2026.

Company-specific interview patterns (2026)

These reflect recent feedback from engineers we've placed. Patterns shift every cycle, but the fundamentals hold.

- NVIDIA — Heavy on debug scenarios and functional coverage strategy. They'll show you a real coverage report and ask you to analyze it. Prep: do coverage closure on your own testbench end-to-end at least once.

- Qualcomm — UVM architecture depth. Expect to whiteboard a full testbench architecture for a block like an AXI interconnect or a DDR controller. Prep: practice drawing testbench block diagrams from memory.

- Intel — Fundamentals + methodology rigor. Intel loves questions about metastability, CDC verification, and formal verification adjacencies. Prep: know clock domain crossing verification patterns.

- Broadcom — Protocol depth. If you're interviewing for a networking block, expect PCIe, Ethernet, or switch-fabric protocol grilling. Prep: pick the protocol the team uses and read the spec, not just summaries.

- Cadence and Synopsys — EDA-flavored questions. How does your sim tool implement assertions? What's LRM vs implementation behavior? These interviews are less about verification craft and more about tool internals. Prep: know your simulator's simulation semantics.

The 6-week prep plan

This is the plan I give to 3-5 year engineers targeting a jump. Adjust for your starting point.

Weeks 1-2: Fundamentals audit

Read through the IEEE 1800 SystemVerilog LRM sections on classes, randomization, and constraints. Not just docs — the actual LRM. You'll find three things you were doing wrong. Fix those in your current testbench.

Read the Accellera UVM 1.2 reference manual, specifically the phasing and config_db sections. If you haven't read them end-to-end before, this is the week.

Weeks 3-4: Project deep-dive prep

Pick your strongest project. Write a one-page summary: architecture, your specific contribution, the bug you're most proud of finding, and one tradeoff you made that you'd defend in an interview. Practice telling this story in 3 minutes to a colleague. Iterate until the delivery is crisp.

Build a GitHub repo with a mini UVM testbench if you don't have public work. A small testbench for a FIFO with full UVM architecture and 90%+ coverage is enough — it signals you can actually write it, not just describe it.

Weeks 5-6: Mock interviews and debug practice

Three mock interviews minimum, ideally with people who actually interview at product companies. Ask for hard feedback.

Take an open-source UVM testbench. Break it deliberately — swap two signals in the interface, make the monitor sample at the wrong edge, introduce a coverage blindspot. Fix each one while narrating your debug process. This builds the muscle that Round 3 tests.

Salary expectations for 3-5 year verification engineers (2026)

India verification compensation has stabilized after the 2024-25 surge. Current ranges for a 3-5 year engineer switching companies:

- Service companies (LTTS, Wipro VLSI, HCL): 8-14 LPA

- Mid-tier product (Cadence, Synopsys, Mentor): 18-28 LPA

- Top-tier product (Intel, Qualcomm, Broadcom, Samsung): 25-40 LPA

- Hyper-growth (NVIDIA, AMD, select startups): 32-55 LPA

These are CTC including stock. Base typically 70-80% of CTC at Indian entities. For the full breakdown across specializations and levels, see our VLSI engineer salary guide 2026.

If you're in the service-company band and have 3-5 years of real tapeout experience, you are undervalued. Practicing interviews seriously for 6 weeks can unlock a 2-3x jump. This is the single highest-leverage career move in VLSI in 2026.

The one mistake that costs more offers than any other

Showing up to a product-company verification interview without a clean 3-minute story about your most recent project.

I've rejected brilliant engineers who couldn't articulate what they'd built. I've hired average engineers who could. The project story is what interviewers remember when they debrief. Get yours right.

Start your prep this week. Browse current verification openings to see what companies are actually hiring for. Match your resume and your story to what's in the job descriptions. Then apply.

Related reading

Frequently asked questions

What are the most common UVM interview questions at product companies in India?

The top five UVM questions I've seen across Intel, Qualcomm, NVIDIA, Broadcom and Cadence interviews in 2026 are: (1) Walk through UVM phases and explain why run_phase is the only time-consuming phase; (2) Explain the factory override mechanism and when you'd use it; (3) Difference between uvm_config_db and uvm_resource_db; (4) How does sequencer-driver handshaking work with get_next_item and item_done; (5) How do you debug a hung testbench. Depth on fewer topics beats surface knowledge of many.

How should a 3-5 year verification engineer prepare differently from a fresher?

Freshers are tested on fundamentals and syntax. Mid-level engineers (3-5 years) are tested on project depth, debug instinct, and verification strategy. The differentiator at this level is a clean 3-minute project story with specifics: what you built, a bug you found that designers pushed back on, and a tradeoff you'd defend. Most mid-level candidates still prep like freshers and get rejected. Stop practicing syntax. Practice debug and project storytelling.

Which simulator should I learn — VCS, Xcelium, or Questa?

Learn the one your target company uses. Qualcomm, Broadcom, AMD are primarily Synopsys VCS. Intel, NVIDIA, Cadence use Cadence Xcelium. Mentor Questa is common at service companies and automotive. You need one deeply — not all three at surface level. Depth means you can explain debug flow, coverage collection, and regression setup from memory.

What salary should a 3-5 year verification engineer expect in India in 2026?

Service companies (LTTS, Wipro VLSI, HCL) pay 8-14 LPA. Mid-tier product companies (Cadence, Synopsys, Mentor) pay 18-28 LPA. Top-tier product companies (Intel, Qualcomm, Broadcom, Samsung) pay 25-40 LPA. Hyper-growth (NVIDIA, AMD) reaches 32-55 LPA. All figures are total CTC including stock. Engineers in the service-company band with real tapeout experience are undervalued and can unlock 2-3x jumps through serious interview prep.

How long should I prepare for a verification engineer interview at a product company?

Six weeks of focused prep is the sweet spot for a 3-5 year engineer. Weeks 1-2: audit fundamentals against the IEEE 1800 LRM and Accellera UVM 1.2 reference. Weeks 3-4: build your project story and a small public UVM testbench on GitHub. Weeks 5-6: three mock interviews and deliberate debug practice on an open-source testbench you break yourself. Less than 4 weeks and you'll bomb Round 3. More than 8 weeks of study with no mock interviews is diminishing returns.

Is formal verification or emulation experience valuable for a verification interview?

It's a significant edge but not a requirement. Formal verification experience is most valued at Intel, Cadence, and Synopsys — where verification teams increasingly own SVA properties for key blocks. Emulation (Palladium, ZeBu, Veloce) is most valued at NVIDIA, Qualcomm, and Samsung, where SoC-scale pre-silicon validation runs on emulators. If you have either, lead with it in your project story. If you don't, don't fake it — interviewers will probe and catch you. Build depth in simulation-based UVM first.